|

|

硬件架构分析

|

|

|

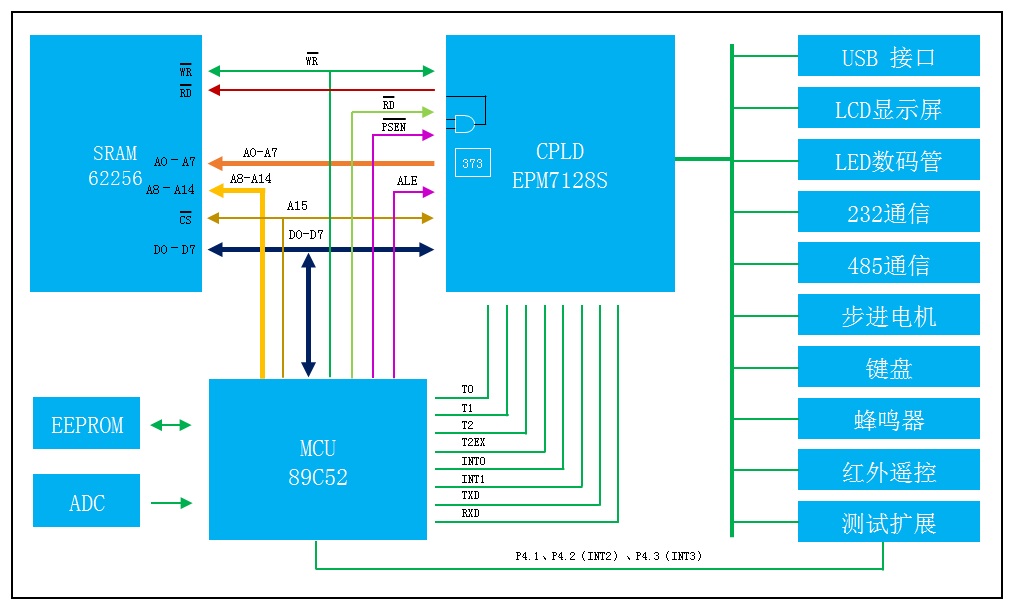

如 图(1) 所示,实验板以89C52和EPM7128S为核心搭建而成,其中89C52作为主处理器存在,而EPM7128S桥接了存贮器和外设,起到了南北桥的作用。89C52的外部总线以及特殊功能信号与EPM7128S对接,以实现两个芯片之间灵活的信号交互。板上集成有一片32K字节容量的随机存贮器 -- 62256。该存贮器挂接在由89C52和EPM7128S共同构建的总线上。地址线A15作为62256的片选信号,决定了62256的地址位于0x0000 - 0x7FFF的32K寻址空间上。同时,A15地址信号也送给了EPM7128S,这样就把0x8000 - 0xFFFF的寻址空间留给了EPM7128S,由EPM7128S进一步分配给每个外设。 |

|

| 图(1) |

|

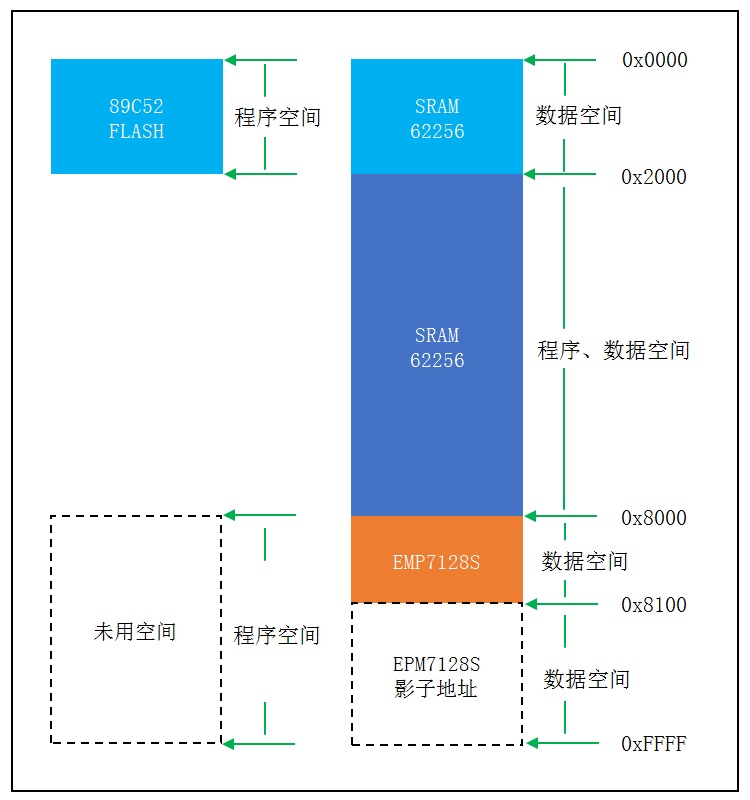

存贮器62256的读信号由89C52的PSEN和RD信号相"与"产生,所以对片外程序的取指操作也能访问到62256,也就是所谓的冯.诺依曼结构。这种结构决定了,我们可以在62256中调试应用程序。 |

|

| 图(2) |

|

不过,并不是整个的62256的存贮空间都是冯.诺认曼寻址的。因为89C52在最低8K程序空间内取址时是不送出PSEN信号的,所以62256最低8K的存贮空间只能存贮数据而不能运行程序。这也是为什么我们调试程序时,要以0x2000做为程序的起始地址。程序空间最低8K的代码存贮在89C52内部的Flash存贮器中。通常,我们把调试代理程序存贮在这一空间上,由调试代理程序调试存贮在62256中的应用程序。调试好后,再把应用程序编译到最低8K的程序空间上,并烧写到89C52的Flash中运行。 |

|

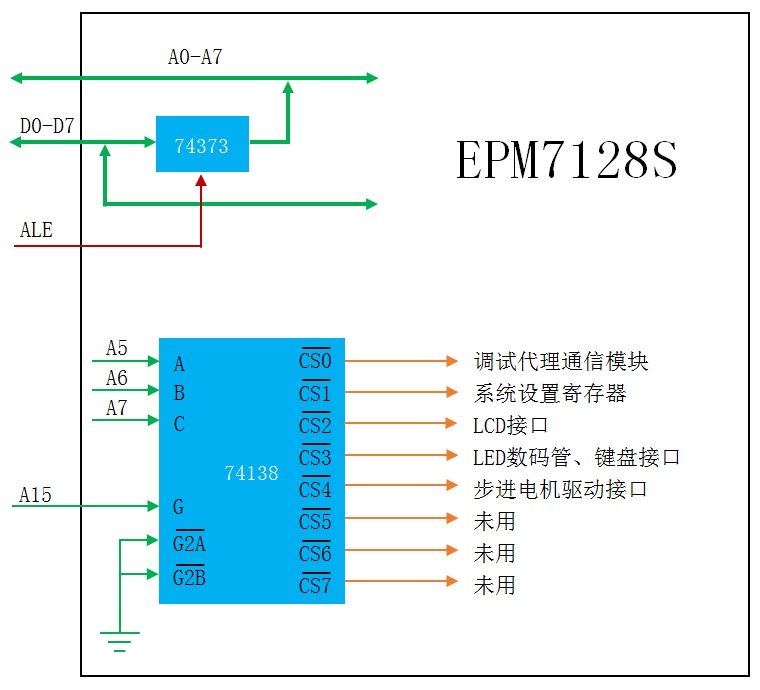

通常在单片机系统中,寻址空间可由74138来分配。在EPM7128S中也同样可使用74138。在出厂逻辑中,就是由一个74138逻辑单元给各个外设接口分配片选信号。 |

|

| 图(3) |

|

74138又称3-8译码器,顾名思义,它可以把3条地址线译成8个片选信号。其实,如果再加上3个使能信号,74138可以对6路输入信号进行译码。在出厂逻辑中,74138的输入信号有4个,分别是A15、A7、A6、A5。其中,A15接使能信号G,当A15为"1"时74138被选中。这就决定了74138的译码范围,只在地址空间0x8000-0xFFFF上有效。地址信号A7、A6、A5分别接地址输入端子C、B、A,这样,输出的片选信号对应的地址段如表(1)所示。每个地址段中包含32个地址,这32个地址由A5-A0加以区分。因为A14-A8并未参与地址译码,所以不可避免的会产生影子地址。所谓"影子地址"就是指给寄存分配的地址不唯一。例如,给某个寄存器分配了表(1)中的0x8000地址,对于这个寄存器来说,通过地址0x8100也可以访问。影子地址是由于对地址信号的不完备译码产生的,虽然表面上浪费的地址空间,但并不影系统的正常工作,还可以减化逻辑电路。 |

|

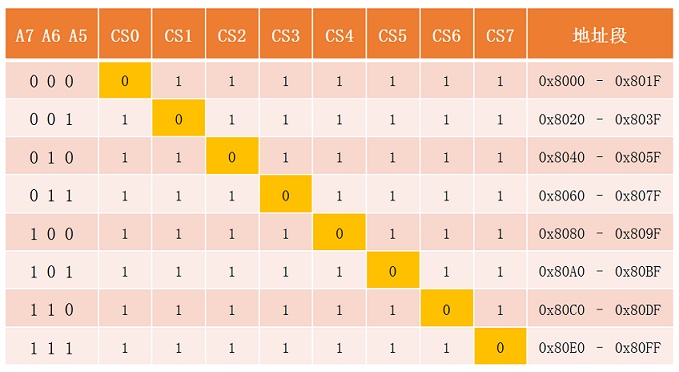

| 表(1) |

|

在出厂逻辑中,CS0用来选通调试代理的通信模块,CS1选通系统设置寄存器,CS2用于LCD接口,CS3用于LED数码管和键盘接口,CS4用在步进电机接口,详见对应的例程。 |

|

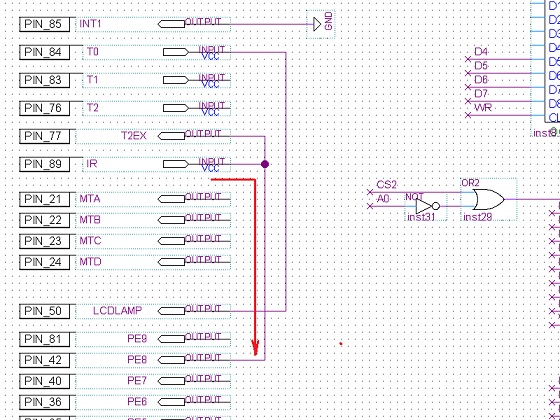

89C52的特殊功能引脚:T0、T1、T2、T2EX、INT0、INT1、RXD以及TXD都与EPM7128S相连,以方便这些功能引脚与EPM7128S内部逻辑交换信号,使89C52内部外设电路与EPM7128S中的逻辑电路融为一体。具体如何使用这些信号,由使用者设计EPM7128S中的逻辑电路来决定。EPM7128S是可编程逻辑器件,内部逻辑可以通过编程来重构,这就决定了实验板的功能具有灵活多变的特性。在出厂的逻辑设计中,INT0被用作了调试代理的数据接收中断信号,T2EX被用来采集红外接收头的信号,T0控制LCD背光开与关,其余信号闲置未用。 |

|

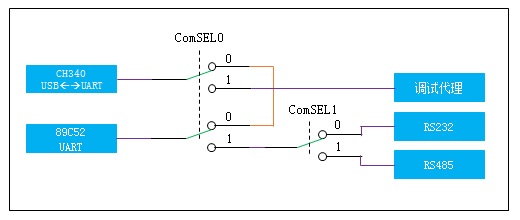

将89C52的UART通信口计算在内,EPM7128S管理着4个通信口。另外3个分别是RS485通信口、RS232通信口、USB通信口。如何在它们之间进行互连由EPM7128S中的逻辑电路决定。在出厂逻辑中,它们的关系如图(3)所示。其中,ComSEL0和ComSEL1是系统控制寄存器中的两个控制位。上电时,ComSEL0和ComSEL1的值都是"0",所以重新上电后89C52的UART与CH340相连,使得ISP工具软件可以通过USB口下载程序到89C52中。上电后若没有ISP工具软件与89C52握手,89C52便启动Flash中的程序。若此时存贮在89C52的Flash中的程序是调试代理,则调试代理会将ComSEL0置"1"。于是CH340便连接到了调试代理的通信口,使得调试代理可以通过USB口与 Keil uVision 通信,实现调试功能。当选择CH340连接到调试代理通信口时,89C52的UART便切换到了ComSEL1开关,由ComSEL1来选择连接RS232还是RS485。当然,如果应用程序在89C52的Flash中运行,也可以设置ComSEL0为"0",然后通过USB口与上位机通信。 |

|

| 图(4) |

|

在51单片机的总线上挂接外设接口,通常要使用74377、74244、74373芯片。74377是8位寄存器芯片,用于实现输出寄存器。74244是8位三态门,用于实现输入寄存器。74373是带输出使能的8位锁存器,当需要实现双向接口时,可以使用74373和74244搭配来实现。 |

|

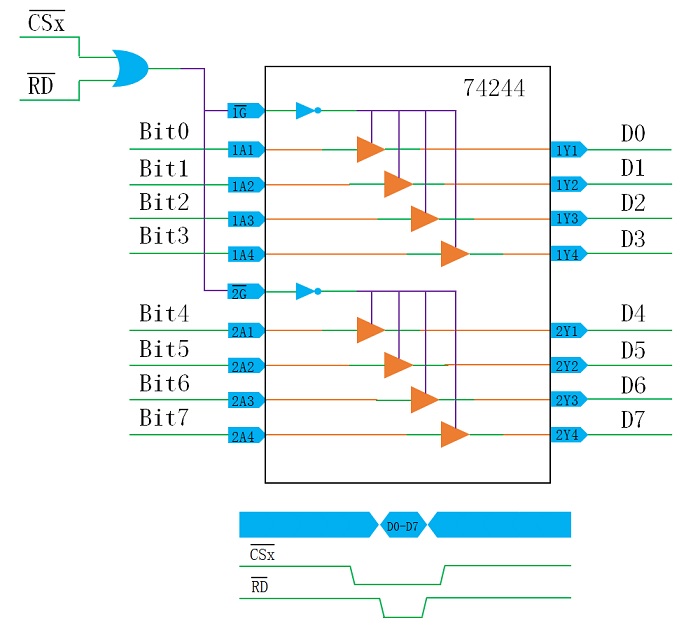

使用74244来实现输入寄存器时,其门控端信号通常来自片选信号CSx和读信号RD的"或"运算。在CSx和RD都为低电平时,74244的三态门将输入信号送到总线上,以供CPU读取。在CSx不为"0"或RD不为"0"时,74244的态门输出高阻、释放总线,以便其它接口的数据在总线上传输。 |

|

| 图(5) |

|

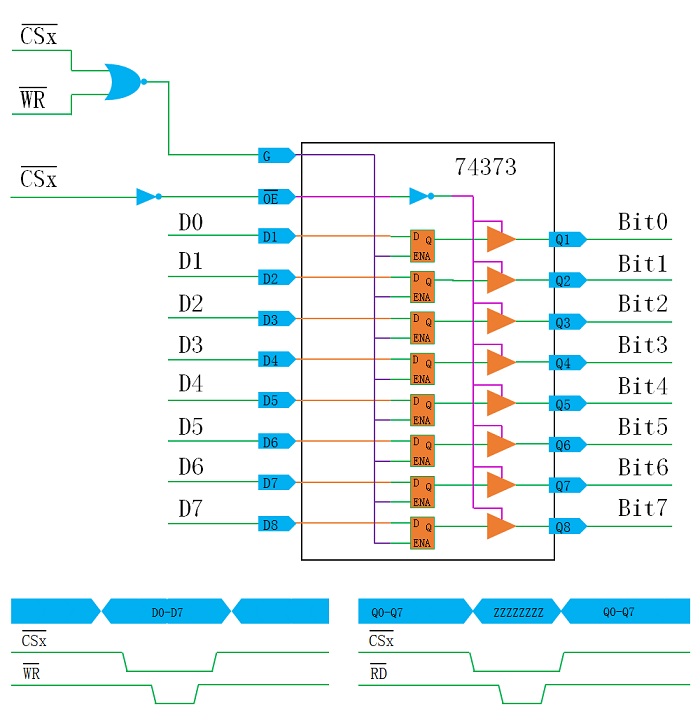

使用74377实现输出寄存器时,其使能端子由片选信号CSx驱动,时钟端子CLK由WR信号驱动,于是在CSx为低电平时,由WR的上升沿把数据总线上的数据锁存到74377的寄存器中,完成写操作。 |

|

| 图(5) |

|

由于74373带有输出门控,适合用来实现双向端口的输出部分。74373的输入数据在G信号的下降沿锁存到寄存器中,所以,由CSx和WR的"或非”运算来驱动G端子。在CSx有效时,由WR的上升沿锁存数据,完成写操作。片选信号CSx信号经过"非"运算驱动OE端子。因此,当CSx有效时74373输出高阻,以便接口的输入数据能够在读信RD的驱动下由74244送到数据总线上,完成读操作。 |

|

| 图(6) |

|

在使用EPM7128S来实现总线接口时,同样会用到这三种逻辑单元,用法类似74系列芯片。不过,在使用74244上略有差别。在使用的独立的74系列芯片来实现总线接口时,可以为每个输入寄存器使用一片74244芯片。而在EPM7128S中,内部逻辑电路是不具有三态门逻辑的,只有在引脚上具有三态门逻辑功能。所以,在EPM7128S中实输入寄存器时,通常使用多路选择器把各个输入寄存器汇总到一起,然后统一使用一个74244挂接在片外的总线上。当然,形式上也可以在原理图上放置多个74244单元,但分析综合器最终在编译的时候还会使用多路选择器来组织它们,然使用一组三态门作为统一的出口。 |

|

| 图(7) |

|

在出厂的逻辑中,输入端口有三个,分别是调试代理通信模块、LCD接口和键盘输入接口。这三个接口通过多路选择口汇总后由74244挂接在总线上。 |

|

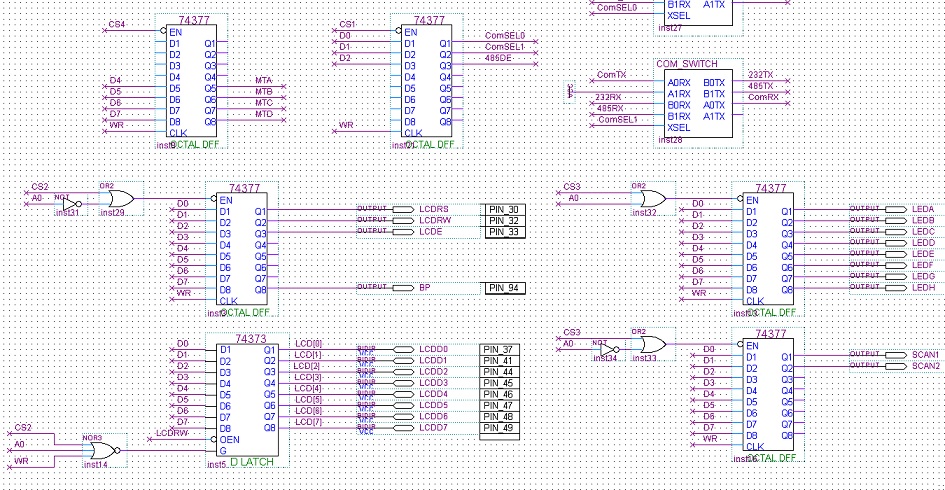

在EPM7128S中同样可以使用74377来实现输出端口。在出厂逻辑中,输出端口有LED数码管的段码寄存器、扫描控制信号寄存器、LCD控制信号寄存器、步进电机控制信号寄存器以及系统控制信号寄存器。这些寄存器都是由74377实现的。LCD接口的数据端口是一个双向端口,所以它的输出部分是由一个74373来实现的。 |

|

| 图(8) |

|

实验板上预留了一个测试扩展接口,该接口的信号从EPM7128S引出。该接接没有预设功能,它的用途完全由使用者决定。一个特别有用的功能是可以从该端口引出EPM7128Sm内部的信号,来观测EPM7128S内部逻辑的行为。这相当于预留了10个可编程测试点。比如,红外接收头送来的信号接到T2EX的同时也引到PE8上,这样在使用T2EX接收这一信号的同时,还可以用示波的探头在PE8的端子上方便的看到这一信号。 |

|

| 图(9) |

|

实验板上所选用的89C52是一款增强功能的51兼容芯片,该芯片具P4端口。其中的P4.1、P4.2、P4.3通过硬件连线连接到了测试扩展口的PE7、PE8、PE9端子上。使用者可以通过PE7、PE8、PE9输出这三个口位的信号,也可以向这三个口位输入信号,还可以将这三个口位与EPM7128S相连接。 |

|

|

|